- 您现在的位置:买卖IC网 > Sheet目录3862 > PIC16F916-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX14 28QFN

197

8018P–AVR–08/10

ATmega169P

Receiver will generate a parity value for the incoming data and compare it to the UPM0n setting.

If a mismatch is detected, the UPEn Flag in UCSRnA will be set.

Bit 3 – USBSn: Stop Bit Select

This bit selects the number of stop bits to be inserted by the Transmitter. The Receiver ignores

this setting.

Bit 2:1 – UCSZn[1:0]: Character Size

The UCSZn[1:0] bits combined with the UCSZn2 bit in UCSRnB sets the number of data bits

(Character SiZe) in a frame the Receiver and Transmitter use.

Bit 0 – UCPOLn: Clock Polarity

This bit is used for synchronous mode only. Write this bit to zero when asynchronous mode is

used. The UCPOLn bit sets the relationship between data output change and data input sample,

and the synchronous clock (XCK).

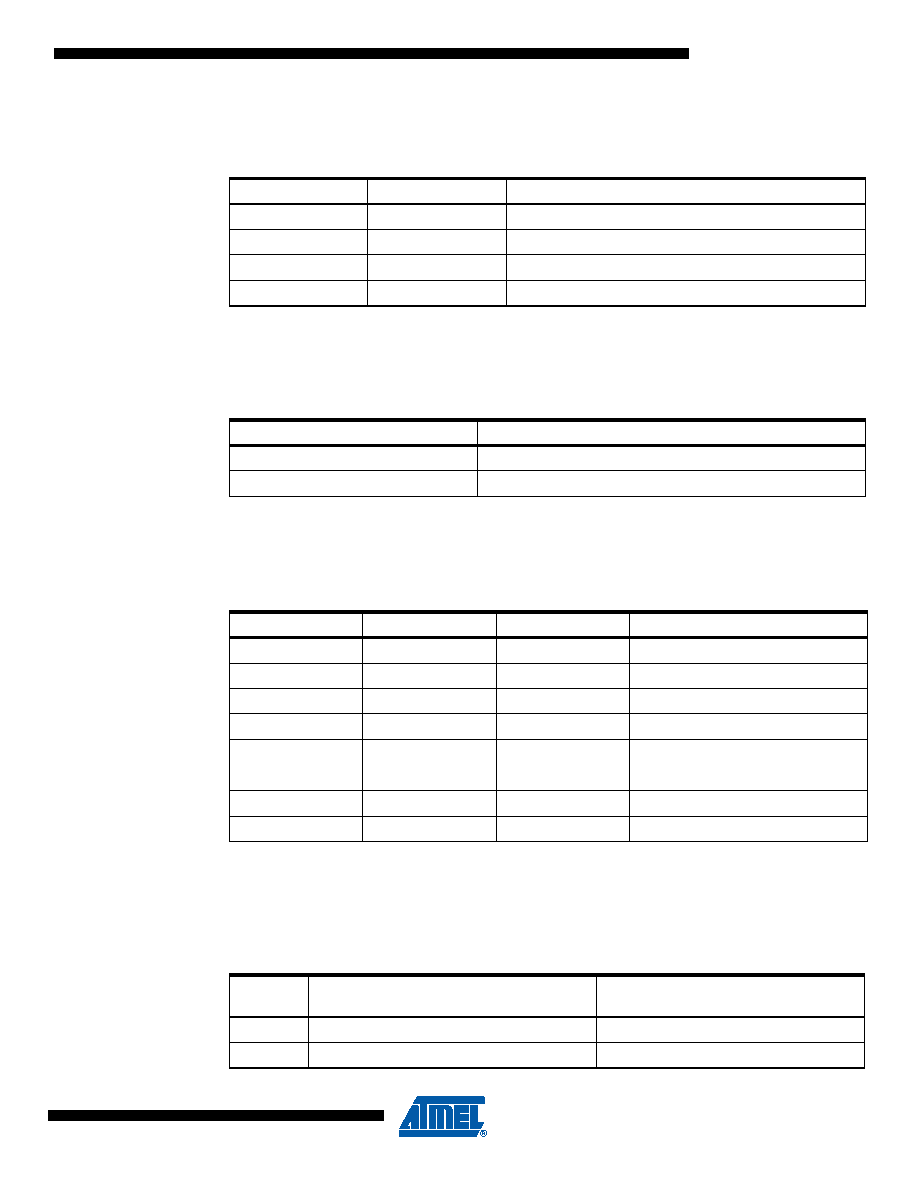

Table 19-9.

UPM Bits Settings

UPMn1

UPMn0

Parity Mode

00

Disabled

01

Reserved

1

0

Enabled, Even Parity

1

Enabled, Odd Parity

Table 19-10. USBSn Bit Settings

USBSn

Stop Bit(s)

01-bit

12-bit

Table 19-11. UCSZ Bits Settings

UCSZn2

UCSZn1

UCSZn0

Character Size

0

5-bit

0

1

6-bit

0

1

0

7-bit

0

1

8-bit

100

Reserved

101

Reserved

110

Reserved

1

9-bit

Table 19-12. UCPOLn Bit Settings

UCPOLn

Transmitted Data Changed

(Output of TxD Pin)

Received Data Sampled (Input on RxD

Pin)

0

Rising XCK Edge

Falling XCK Edge

1

Falling XCK Edge

Rising XCK Edge

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C716-20I/P

IC MCU OTP 2KX14 A/D PWM 18DIP

PIC18F26K80-I/SO

MCU PIC 64KB FLASH 28SOIC

PIC18F26J13-I/SS

IC PIC MCU 64KB FLASH 28SSOP

SFW27R-1STE1

SFW27R-1STE1-FFC/FPC CONN

PIC18F66J15-I/PT

IC PIC MCU FLASH 48KX16 64TQFP

PIC24FV32KA302-I/SO

MCU 32KB FLASH 2KB RAM 28-SOIC

PIC24HJ64GP204-I/ML

IC PIC MCU FLASH 64K 44-QFN

SFW27R-2STE1

SFW27R-2STE1-FFC/FPC CONN

相关代理商/技术参数

PIC16F916-I/SO

功能描述:8位微控制器 -MCU 14KB FL 352R 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F916-I/SO

制造商:Microchip Technology Inc 功能描述:8 Bit Microcontroller Clock Speed:20MHz

PIC16F916-I/SOG

制造商:Microchip Technology Inc 功能描述:8BIT MCU FLASH SMD 16F916 SOIC28

PIC16F916-I/SP

功能描述:8位微控制器 -MCU 14KB FL 352R 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F916-I/SP

制造商:Microchip Technology Inc 功能描述:8 Bit Microcontroller Clock Speed:20MHz

PIC16F916-I/SS

功能描述:8位微控制器 -MCU 14KB FL 352R 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F916-I/SS

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC16F916T-E/MLC02

制造商:Microchip Technology Inc 功能描述: